axis_xgmii_tx_64

- File: axis_xgmii_tx_64_code

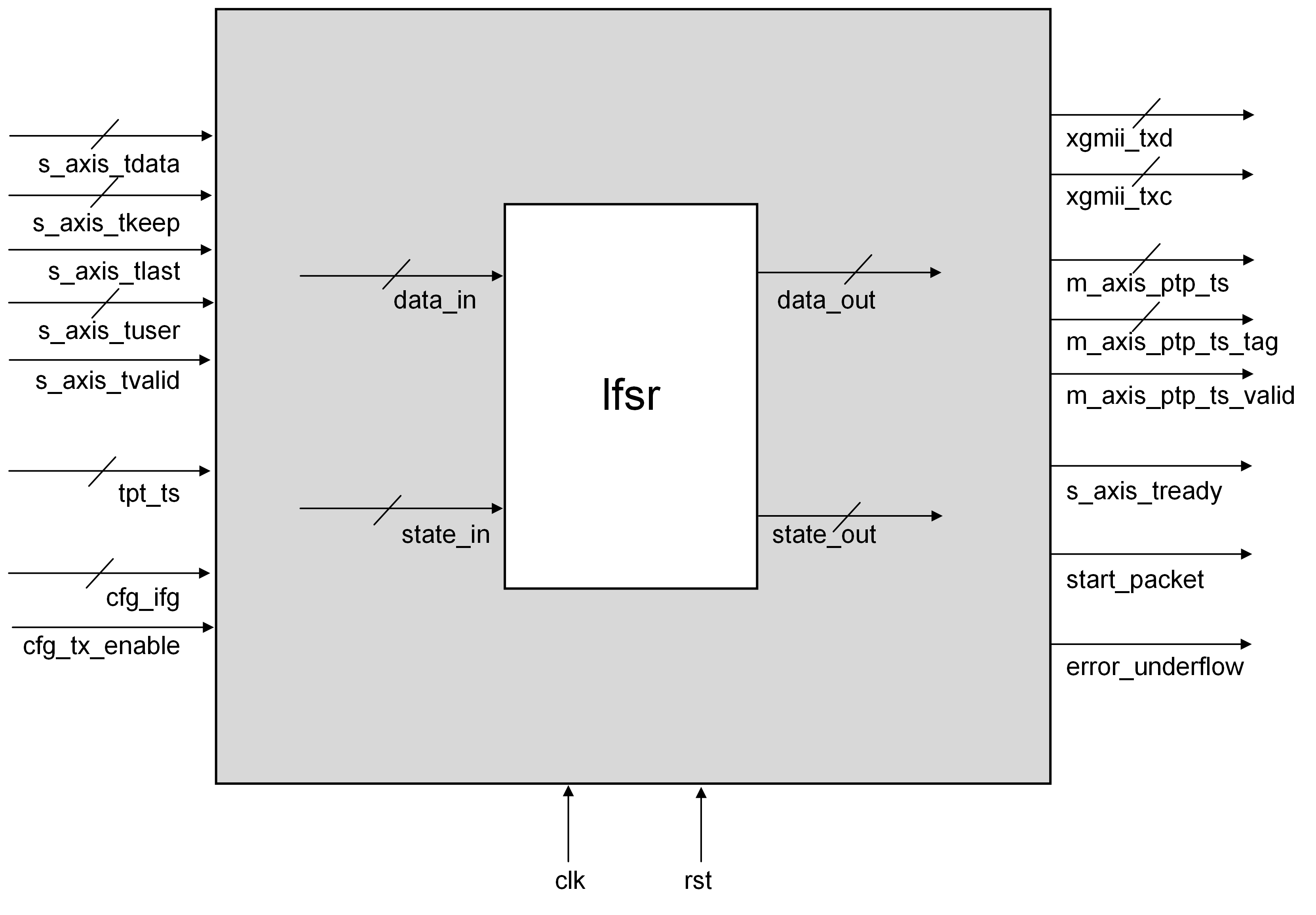

Diagram

Hierarchical structure

Description

Modulo que convierte interfaz AXI a XGMII

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| DATA_WIDTH | 64 | Parametro que define el tamaño de los datos | |

| KEEP_WIDTH | (DATA_WIDTH/8) | Cantidad de bytes de datos que deben ser válidos | |

| CTRL_WIDTH | (DATA_WIDTH/8) | Cantidad de bits de control | |

| ENABLE_PADDING | 1 | Flag para habilitar el relleno de tramas | |

| ENABLE_DIC | 1 | Flag para habilitar DIC | |

| MIN_FRAME_LENGTH | 64 | Longitud mínima de la trama | |

| PTP_TS_ENABLE | 0 | Flag para habilitar protocolo PTP | |

| PTP_TS_FMT_TOD | 1 | Flag para cambiar el formato de la marca de tiempo según "Time of day" | |

| PTP_TS_WIDTH | PTP_TS_FMT_TOD ? 96 : 64 | Parametro del ancho de la marca del tiempo | |

| PTP_TS_CTRL_IN_TUSER | 0 | Flag para habilitar control PTP en tuser | |

| PTP_TAG_ENABLE | PTP_TS_ENABLE | Flag para habilitar etiqueta PTP | |

| PTP_TAG_WIDTH | 16 | Ancho de la etiqueta PTP | |

| USER_WIDTH | (PTP_TS_ENABLE ? | Parametro que define el ancho de los datos de usuario |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| clk | input | wire | Señal de clock |

| rst | input | wire | Señal de reset |

| s_axis_tdata | input | wire [DATA_WIDTH-1:0] | Entrada de datos de la interfaz AXI |

| s_axis_tkeep | input | wire [KEEP_WIDTH-1:0] | Entrada de bits válidos de la interfaz AXI |

| s_axis_tvalid | input | wire | Señal de datos válidos de la interfaz AXI |

| s_axis_tready | output | wire | Señal de que la interfaz AXI está lista para recibir datos |

| s_axis_tlast | input | wire | Señal de fin de trama de la interfaz AXI |

| s_axis_tuser | input | wire [USER_WIDTH-1:0] | Entrada de datos de usuario de la interfaz AXI |

| xgmii_txd | output | wire [DATA_WIDTH-1:0] | Salida de datos de la interfaz XGMII |

| xgmii_txc | output | wire [CTRL_WIDTH-1:0] | Salida de control de la interfaz XGMII |

| ptp_ts | input | wire [PTP_TS_WIDTH-1:0] | Entrada de marca de tiempo PTP |

| m_axis_ptp_ts | output | wire [PTP_TS_WIDTH-1:0] | Salida de marca de tiempo PTP |

| m_axis_ptp_ts_tag | output | wire [PTP_TAG_WIDTH-1:0] | Salida de etiqueta de marca de tiempo PTP |

| m_axis_ptp_ts_valid | output | wire | Señal de validez de marca de tiempo PTP |

| cfg_ifg | input | wire [7:0] | Señal de configuración de espacio interframe |

| cfg_tx_enable | input | wire | Señal de configuración para habilitar transmisión |

| start_packet | output | wire [1:0] | Estado indicando inicio de paquete |

| error_underflow | output | wire | Señal de error por desbordamiento |

Signals

| Name | Type | Description |

|---|---|---|

| state_reg = STATE_IDLE | reg [2:0] | Registro y próximo estado del FSM |

| state_next | reg [2:0] | Registro y próximo estado del FSM |

| reset_crc | reg | Señal para resetear el CRC |

| update_crc | reg | Señal para actualizar el CRC |

| swap_lanes_reg = 1'b0 | reg | Registro y próximo valor de swap de lanes |

| swap_lanes_next | reg | Registro y próximo valor de swap de lanes |

| swap_txd = 32'd0 | reg [31:0] | Datos para swap de lanes |

| swap_txc = 4'd0 | reg [3:0] | Datos de control para swap de lanes |

| s_axis_tdata_masked | reg [DATA_WIDTH-1:0] | Datos de la entrada AXI con máscara aplicada |

| s_tdata_reg = 0 | reg [DATA_WIDTH-1:0] | Registro y próximo valor de datos de entrada AXI |

| s_tdata_next | reg [DATA_WIDTH-1:0] | Registro y próximo valor de datos de entrada AXI |

| s_empty_reg = 0 | reg [EMPTY_WIDTH-1:0] | Registro y próximo valor de datos vacíos |

| s_empty_next | reg [EMPTY_WIDTH-1:0] | Registro y próximo valor de datos vacíos |

| fcs_output_txd_0 | reg [DATA_WIDTH-1:0] | Datos de salida del primer FCS |

| fcs_output_txd_1 | reg [DATA_WIDTH-1:0] | Datos de salida del segundo FCS |

| fcs_output_txc_0 | reg [CTRL_WIDTH-1:0] | Control de salida del primer FCS |

| fcs_output_txc_1 | reg [CTRL_WIDTH-1:0] | Control de salida del segundo FCS |

| ifg_offset | reg [7:0] | Desplazamiento para el intervalo entre tramas |

| frame_start_reg = 1'b0 | reg | Registro y próximo valor de inicio de trama |

| frame_start_next | reg | Registro y próximo valor de inicio de trama |

| frame_reg = 1'b0 | reg | Registro y próximo valor de trama |

| frame_next | reg | Registro y próximo valor de trama |

| frame_error_reg = 1'b0 | reg | Registro y próximo valor de error de trama |

| frame_error_next | reg | Registro y próximo valor de error de trama |

| frame_min_count_reg = 0 | reg [MIN_LEN_WIDTH-1:0] | Registro y próximo valor de contador de longitud mínima de trama |

| frame_min_count_next | reg [MIN_LEN_WIDTH-1:0] | Registro y próximo valor de contador de longitud mínima de trama |

| ifg_count_reg = 8'd0 | reg [7:0] | Registro y próximo valor de contador de intervalo entre tramas |

| ifg_count_next | reg [7:0] | Registro y próximo valor de contador de intervalo entre tramas |

| deficit_idle_count_reg = 2'd0 | reg [1:0] | Registro y próximo valor de contador de déficit de inactividad |

| deficit_idle_count_next | reg [1:0] | Registro y próximo valor de contador de déficit de inactividad |

| s_axis_tready_reg = 1'b0 | reg | Registro y próximo valor de disponibilidad de AXI |

| s_axis_tready_next | reg | Registro y próximo valor de disponibilidad de AXI |

| m_axis_ptp_ts_reg = 0 | reg [PTP_TS_WIDTH-1:0] | Registro de marca de tiempo PTP |

| m_axis_ptp_ts_adj_reg = 0 | reg [PTP_TS_WIDTH-1:0] | Registro de ajuste de marca de tiempo PTP |

| m_axis_ptp_ts_tag_reg = 0 | reg [PTP_TAG_WIDTH-1:0] | Registro de etiqueta de marca de tiempo PTP |

| m_axis_ptp_ts_valid_reg = 1'b0 | reg | Registro de validez de marca de tiempo PTP |

| m_axis_ptp_ts_valid_int_reg = 1'b0 | reg | Registro interno de validez de marca de tiempo PTP |

| m_axis_ptp_ts_borrow_reg = 1'b0 | reg | Registro de ajuste de marca de tiempo PTP |

| crc_state_reg[7:0] | reg [31:0] | Registro de estado de CRC |

| crc_state_next[7:0] | wire [31:0] | Próximo valor del estado de CRC |

| last_ts_reg = 0 | reg [4+16-1:0] | Registro del último timestamp |

| ts_inc_reg = 0 | reg [4+16-1:0] | Registro de incremento del timestamp |

| xgmii_txd_reg = {CTRL_WIDTH{XGMII_IDLE}} | reg [DATA_WIDTH-1:0] | Registro y próximo valor de datos XGMII |

| xgmii_txd_next | reg [DATA_WIDTH-1:0] | Registro y próximo valor de datos XGMII |

| xgmii_txc_reg = {CTRL_WIDTH{1'b1}} | reg [CTRL_WIDTH-1:0] | Registro y próximo valor de control XGMII |

| xgmii_txc_next | reg [CTRL_WIDTH-1:0] | Registro y próximo valor de control XGMII |

| start_packet_reg = 2'b00 | reg | Registro de inicio de paquete |

| error_underflow_reg = 1'b0 | reg | Registro y próximo valor de error por desbordamiento |

| error_underflow_next | reg | Registro y próximo valor de error por desbordamiento |

| j | integer |

Constants

| Name | Type | Value | Description |

|---|---|---|---|

| EMPTY_WIDTH | $ | Parametro del ancho de vacío | |

| MIN_LEN_WIDTH | $ | Parametro del ancho mínimo de la longitud | |

| ETH_PRE | 8'h55 | Preambulo de Ethernet | |

| ETH_SFD | 8'hD5 | Delimitador de inicio de trama de Ethernet | |

| XGMII_IDLE | 8'h07 | Código de control de XGMII para estado IDLE | |

| XGMII_START | 8'hfb | Código de control de XGMII para inicio de paquete | |

| XGMII_TERM | 8'hfd | Código de control de XGMII para terminación de paquete | |

| XGMII_ERROR | 8'hfe | Código de control de XGMII para error | |

| STATE_IDLE | 3'd0 | Estado IDLE | |

| STATE_PAYLOAD | 3'd1 | Estado PAYLOAD | |

| STATE_PAD | 3'd2 | Estado PAD | |

| STATE_FCS_1 | 3'd3 | Estado FCS__1 | |

| STATE_FCS_2 | 3'd4 | Estado FCS__2 | |

| STATE_ERR | 3'd5 | Estado ERR | |

| STATE_IFG | 3'd6 | Estado IFG |

Functions

- keep2empty

- Convierte un byte de control k de 8 bits a un valor de 3 bits que representa el número de bits vacíos (no válidos) en el byte

Processes

- unnamed: ( @* )

- Type: always

- Description

Aplica mascara a los datos de entrada

- unnamed: ( @* )

- Type: always

- Description

Calculo del ciclo FCS

- unnamed: ( @* )

- Type: always

- Description

Define una combinación de asignaciones y lógica de control que determina el comportamiento de un sistema de transmisión de datos

- unnamed: ( @(posedge clk) )

- Type: always

- Description

Actualiza registros de control y datos, gestiona la marca de tiempo PTP y el estado del CRC, y controla la transmisión de datos a través del medio físico

Instantiations

State machines

- Define una combinación de asignaciones y lógica de control que determina el comportamiento de un sistema de transmisión de datos

state transitions cluster_state_next state_next STATE_IDLE STATE_IDLE STATE_IDLE->STATE_IDLE not (s_axis_tvalid && s_axis_tready) STATE_PAYLOAD STATE_PAYLOAD STATE_IDLE->STATE_PAYLOAD s_axis_tvalid && s_axis_tready STATE_PAYLOAD->STATE_PAYLOAD not (!s_axis_tvalid || s_axis_tlast) STATE_PAD STATE_PAD STATE_PAYLOAD->STATE_PAD frame_min_count_reg > CTRL_WIDTH ENABLE_PADDING && frame_min_count_reg !s_axis_tvalid || s_axis_tlast STATE_FCS_1 STATE_FCS_1 STATE_PAYLOAD->STATE_FCS_1 not (ENABLE_PADDING && frame_min_count_reg) not (frame_error_next) !s_axis_tvalid || s_axis_tlast STATE_ERR STATE_ERR STATE_PAYLOAD->STATE_ERR frame_error_next !s_axis_tvalid || s_axis_tlast STATE_PAD->STATE_PAD frame_min_count_reg > CTRL_WIDTH STATE_PAD->STATE_FCS_1 not (frame_error_reg) not (frame_min_count_reg > CTRL_WIDTH) STATE_PAD->STATE_ERR frame_error_reg not (frame_min_count_reg > CTRL_WIDTH) STATE_FCS_2 STATE_FCS_2 STATE_FCS_1->STATE_FCS_2 s_empty_reg <= 4 STATE_IFG STATE_IFG STATE_FCS_1->STATE_IFG not (s_empty_reg <= 4) STATE_FCS_2->STATE_IDLE not (ENABLE_DIC) not (ifg_count_next > 8'd4) STATE_FCS_2->STATE_IFG ifg_count_next > 8'd7 ENABLE_DIC STATE_FCS_2->STATE_IFG ifg_count_next > 8'd4 STATE_IFG->STATE_IDLE not (ENABLE_DIC) not (ifg_count_next > 8'd4 || frame_reg) STATE_IFG->STATE_IFG ifg_count_next > 8'd7 || frame_reg ENABLE_DIC STATE_IFG->STATE_IFG ifg_count_next > 8'd4 || frame_reg