eth_mac_10g

- File: eth_mac_10g_code

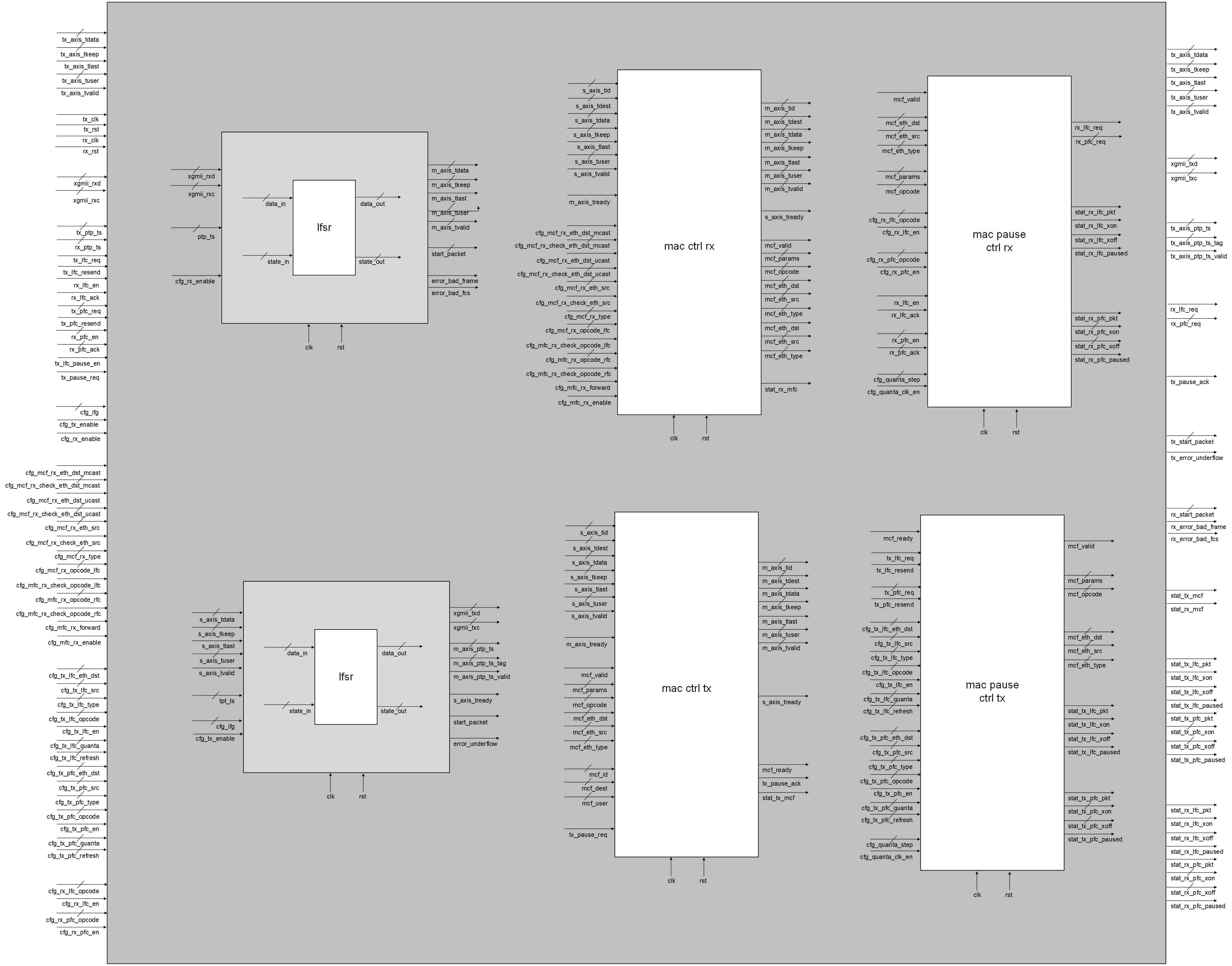

Diagram

Hierarchical structure

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| DATA_WIDTH | 64 | Ancho de datos | |

| KEEP_WIDTH | (DATA_WIDTH/8) | Ancho de bits válidos | |

| CTRL_WIDTH | (DATA_WIDTH/8) | Ancho de control | |

| ENABLE_PADDING | 1 | Flag para habilitar padding | |

| ENABLE_DIC | 1 | Flag para habilitar DIC | |

| MIN_FRAME_LENGTH | 64 | Longitud mínima de trama | |

| PTP_TS_ENABLE | 0 | Flag para habilitar marca de tiempo PTP | |

| PTP_TS_FMT_TOD | 1 | Formato de marca de tiempo PTP | |

| PTP_TS_WIDTH | PTP_TS_FMT_TOD ? 96 : 64 | Ancho de marca de tiempo PTP | |

| TX_PTP_TS_CTRL_IN_TUSER | 0 | Control de marca de tiempo PTP en TUSER | |

| TX_PTP_TAG_ENABLE | PTP_TS_ENABLE | Habilitar etiqueta PTP en transmisión | |

| TX_PTP_TAG_WIDTH | 16 | Ancho de etiqueta PTP en transmisión | |

| TX_USER_WIDTH | (PTP_TS_ENABLE ? (TX_PTP_TAG_ENABLE ? TX_PTP_TAG_WIDTH : 0) + (TX_PTP_TS_CTRL_IN_TUSER ? 1 : 0) : 0) + 1 | Ancho de datos de usuario en transmisión | |

| RX_USER_WIDTH | (PTP_TS_ENABLE ? PTP_TS_WIDTH : 0) + 1 | Ancho de datos de usuario en recepción | |

| PFC_ENABLE | 0 | Flag para habilitar control de flujo prioritario PFC | |

| PAUSE_ENABLE | PFC_ENABLE | Flag para habilitar pausa de control de flujo LFC |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| rx_clk | input | wire | Señal de clock del receptor |

| rx_rst | input | wire | Señal de reset del receptor |

| tx_clk | input | wire | Señal de clock del transmisor |

| tx_rst | input | wire | Señal de reset del transmisor |

| tx_axis_tdata | input | wire [DATA_WIDTH-1:0] | Datos de la interfaz AXI del transmisor |

| tx_axis_tkeep | input | wire [KEEP_WIDTH-1:0] | Bits válidos de la interfaz AXI del transmisor |

| tx_axis_tvalid | input | wire | Señal de datos válidos de la interfaz AXI del transmisor |

| tx_axis_tready | output | wire | Señal de ready de la interfaz AXI del transmisor |

| tx_axis_tlast | input | wire | Señal de fin de trama de la interfaz AXI del transmisor |

| tx_axis_tuser | input | wire [TX_USER_WIDTH-1:0] | Datos de usuario de la interfaz AXI del transmisor |

| rx_axis_tdata | output | wire [DATA_WIDTH-1:0] | Datos de la interfaz AXI del receptor |

| rx_axis_tkeep | output | wire [KEEP_WIDTH-1:0] | Bits válidos de la interfaz AXI del receptor |

| rx_axis_tvalid | output | wire | Señal de datos válidos de la interfaz AXI del receptor |

| rx_axis_tlast | output | wire | Señal de fin de trama de la interfaz AXI del receptor |

| rx_axis_tuser | output | wire [RX_USER_WIDTH-1:0] | Datos de usuario de la interfaz AXI del receptor |

| xgmii_rxd | input | wire [DATA_WIDTH-1:0] | Datos recibidos de la interfaz XGMII |

| xgmii_rxc | input | wire [CTRL_WIDTH-1:0] | Datos de control recibidos de la interfaz XGMII |

| xgmii_txd | output | wire [DATA_WIDTH-1:0] | Datos transmitidos de la interfaz XGMII |

| xgmii_txc | output | wire [CTRL_WIDTH-1:0] | Datos de control transmitidos de la interfaz XGMII |

| tx_ptp_ts | input | wire [PTP_TS_WIDTH-1:0] | Marca de tiempo PTP del transmisor |

| rx_ptp_ts | input | wire [PTP_TS_WIDTH-1:0] | Marca de tiempo PTP del receptor |

| tx_axis_ptp_ts | output | wire [PTP_TS_WIDTH-1:0] | Marca de tiempo PTP en interfaz AXI del transmisor |

| tx_axis_ptp_ts_tag | output | wire [TX_PTP_TAG_WIDTH-1:0] | Etiqueta de marca de tiempo PTP en interfaz AXI del transmisor |

| tx_axis_ptp_ts_valid | output | wire | Señal de datos válidos de marca de tiempo PTP en interfaz AXI del transmisor |

| tx_lfc_req | input | wire | Solicitud de pausa de control de flujo en el transmisor |

| tx_lfc_resend | input | wire | Reenvío de solicitud de pausa de control de flujo en el transmisor |

| rx_lfc_en | input | wire | Habilitación de pausa de control de flujo en el receptor |

| rx_lfc_req | output | wire | Solicitud de pausa de control de flujo en el receptor |

| rx_lfc_ack | input | wire | Reconocimiento de pausa de control de flujo en el receptor |

| tx_pfc_req | input | wire [7:0] | Solicitud de control de flujo prioritario el transmisor |

| tx_pfc_resend | input | wire | Reenvío de solicitud de control de flujo prioritario el transmisor |

| rx_pfc_en | input | wire [7:0] | Habilitación de control de flujo prioritario en el receptor |

| rx_pfc_req | output | wire [7:0] | Solicitud de control de flujo prioritario en el receptor |

| rx_pfc_ack | input | wire [7:0] | Reconocimiento de control de flujo prioritario en el receptor |

| tx_lfc_pause_en | input | wire | Habilitación de pausa de control de flujo el transmisor |

| tx_pause_req | input | wire | Solicitud de pausa el transmisor |

| tx_pause_ack | output | wire | Reconocimiento de pausa el transmisor |

| tx_start_packet | output | wire [1:0] | Estado de inicio de paquete en el transmisor |

| tx_error_underflow | output | wire | Error de subflujo en el transmisor |

| rx_start_packet | output | wire [1:0] | Estado de inicio de paquete en el receptor |

| rx_error_bad_frame | output | wire | Error de trama incorrecta en el receptor |

| rx_error_bad_fcs | output | wire | Error de FCS incorrecto en el receptor |

| stat_tx_mcf | output | wire | Estado que indica la transmisión de un marco de control MAC. |

| stat_rx_mcf | output | wire | Estado que indica la recepción de un marco de control MAC. |

| stat_tx_lfc_pkt | output | wire | Estado que indica la transmisión de un paquete LFC. |

| stat_tx_lfc_xon | output | wire | Estado que indica la transmisión de una señal XON en LFC. |

| stat_tx_lfc_xoff | output | wire | Estado que indica la transmisión de una señal XOFF en LFC. |

| stat_tx_lfc_paused | output | wire | Estado que indica que la transmisión está pausada debido a LFC. |

| stat_tx_pfc_pkt | output | wire | Estado que indica la transmisión de un paquete PFC. |

| stat_tx_pfc_xon | output | wire [7:0] | Estado que indica la transmisión de una señal XON en PFC para cada prioridad. |

| stat_tx_pfc_xoff | output | wire [7:0] | Estado que indica la transmisión de una señal XOFF en PFC para cada prioridad. |

| stat_tx_pfc_paused | output | wire [7:0] | Estado que indica que la transmisión está pausada debido a PFC para cada prioridad. |

| stat_rx_lfc_pkt | output | wire | Estado que indica la recepción de un paquete LFC. |

| stat_rx_lfc_xon | output | wire | Estado que indica la recepción de una señal XON en LFC. |

| stat_rx_lfc_xoff | output | wire | Estado que indica la recepción de una señal XOFF en LFC. |

| stat_rx_lfc_paused | output | wire | Estado que indica que la recepción está pausada debido a LFC. |

| stat_rx_pfc_pkt | output | wire | Estado que indica la recepción de un paquete PFC. |

| stat_rx_pfc_xon | output | wire [7:0] | Estado que indica la recepción de una señal XON en PFC para cada prioridad. |

| stat_rx_pfc_xoff | output | wire [7:0] | Estado que indica la recepción de una señal XOFF en PFC para cada prioridad. |

| stat_rx_pfc_paused | output | wire [7:0] | Estado que indica que la recepción está pausada debido a PFC para cada prioridad. |

| cfg_tx_enable | input | wire | Habilitación del transmisor |

| cfg_rx_enable | input | wire | Habilitación del receptor |

| cfg_mcf_rx_eth_dst_mcast | input | wire [47:0] | Dirección multicast Ethernet del receptor MCF |

| cfg_mcf_rx_check_eth_dst_mcast | input | wire | Verificación de dirección multicast Ethernet del receptor MCF |

| cfg_mcf_rx_eth_dst_ucast | input | wire [47:0] | Dirección unicast Ethernet del receptor MCF |

| cfg_mcf_rx_check_eth_dst_ucast | input | wire | Verificación de dirección unicast Ethernet del receptor MCF |

| cfg_mcf_rx_eth_src | input | wire [47:0] | Dirección de origen Ethernet del receptor MCF |

| cfg_mcf_rx_check_eth_src | input | wire | Verificación de dirección de origen Ethernet del receptor MCF |

| cfg_mcf_rx_eth_type | input | wire [15:0] | Tipo Ethernet del receptor MCF |

| cfg_mcf_rx_opcode_lfc | input | wire [15:0] | Código de operación LFC del receptor MCF |

| cfg_mcf_rx_check_opcode_lfc | input | wire | Verificación de código de operación LFC del receptor MCF |

| cfg_mcf_rx_opcode_pfc | input | wire [15:0] | Código de operación PFC del receptor MCF |

| cfg_mcf_rx_check_opcode_pfc | input | wire | Verificación de código de operación PFC del receptor MCF |

| cfg_mcf_rx_forward | input | wire | Reenvío del receptor MCF |

| cfg_mcf_rx_enable | input | wire | Habilitación del receptor MCF |

| cfg_tx_lfc_eth_dst | input | wire [47:0] | Dirección Ethernet de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_eth_src | input | wire [47:0] | Dirección de origen Ethernet de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_eth_type | input | wire [15:0] | Tipo Ethernet de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_opcode | input | wire [15:0] | Código de operación de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_en | input | wire | Habilitación de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_quanta | input | wire [15:0] | Cuánta de pausa de control de flujo en el transmisor |

| cfg_tx_lfc_refresh | input | wire [15:0] | Actualización de pausa de control de flujo en el transmisor |

| cfg_tx_pfc_eth_dst | input | wire [47:0] | Dirección Ethernet de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_eth_src | input | wire [47:0] | Dirección de origen Ethernet de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_eth_type | input | wire [15:0] | Tipo Ethernet de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_opcode | input | wire [15:0] | Código de operación de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_en | input | wire | Habilitación de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_quanta | input | wire [8*16-1:0] | Cuánta de control de flujo prioritario en el transmisor |

| cfg_tx_pfc_refresh | input | wire [8*16-1:0] | Actualización de control de flujo prioritario en el transmisor |

| cfg_rx_lfc_opcode | input | wire [15:0] | Código de operación de pausa de control de flujo en el receptor |

| cfg_rx_lfc_en | input | wire | Habilitación de pausa de control de flujo en el receptor |

| cfg_rx_pfc_opcode | input | wire [15:0] | Código de operación de control de flujo prioritario en el receptor |

| cfg_rx_pfc_en | input | wire | Habilitación de control de flujo prioritario en el receptor |

Signals

| Name | Type | Description |

|---|---|---|

| tx_axis_tdata_int | wire [DATA_WIDTH-1:0] | Datos de salida internos de la interfaz AXI en el transmisor |

| tx_axis_tkeep_int | wire [KEEP_WIDTH-1:0] | Bits válidos de salida internos de la interfaz AXI en el transmisor |

| tx_axis_tvalid_int | wire | Señal de datos válidos interna de la interfaz AXI en el transmisor |

| tx_axis_tready_int | wire | Flag de ready para recibir datos interna de la interfaz AXI en el transmisor |

| tx_axis_tlast_int | wire | Flag de fin de trama interna de la interfaz AXI en el transmisor |

| tx_axis_tuser_int | wire [TX_USER_WIDTH_INT-1:0] | Datos de usuario internos de la interfaz AXI en el transmisor |

| rx_axis_tdata_int | wire [DATA_WIDTH-1:0] | Datos de entrada internos de la interfaz AXI en el receptor |

| rx_axis_tkeep_int | wire [KEEP_WIDTH-1:0] | Bits válidos de entrada internos de la interfaz AXI en el receptor |

| rx_axis_tvalid_int | wire | Flag de datos válidos interna de la interfaz AXI en el receptor |

| rx_axis_tlast_int | wire | Flag de fin de trama interna de la interfaz AXI en el receptor |

| rx_axis_tuser_int | wire [RX_USER_WIDTH-1:0] | Datos de usuario internos de la interfaz AXI en el receptor |

Constants

| Name | Type | Value | Description |

|---|---|---|---|

| MAC_CTRL_ENABLE | PAUSE_ENABLE | ||

| TX_USER_WIDTH_INT | MAC_CTRL_ENABLE ? (PTP_TS_ENABLE ? (TX_PTP_TAG_ENABLE ? TX_PTP_TAG_WIDTH : 0) + 1 : 0) + 1 : TX_USER_WIDTH | Ancho de datos de usuario interno en transmisión |

Instantiations

-

axis_xgmii_rx_inst: axis_xgmii_rx_64

Description

Instancia un módulo para el receptor que transforma la interfaz XGMII a AXIS -

axis_xgmii_tx_inst: axis_xgmii_tx_64

Description

Instancia un módulo para el transmisor que transforma la interfaz AXIS A XGMII -

mac_ctrl_tx_inst: 10GBASE/MAC/mac_ctrl_tx

Description

Instancia un módulo que controla la transmisión MAC -

mac_ctrl_rx_inst: mac_ctrl_rx

Description

Instancia un módulo que controla la recepción MAC -

mac_pause_ctrl_tx_inst: mac_pause_ctrl_tx

Description

Instancia un módulo que controla el frame de pause de la transmisión MAC -

mac_pause_ctrl_rx_inst: mac_pause_ctrl_rx

Description

Instancia un módulo que controla el frama de pausa de la recepción MAC