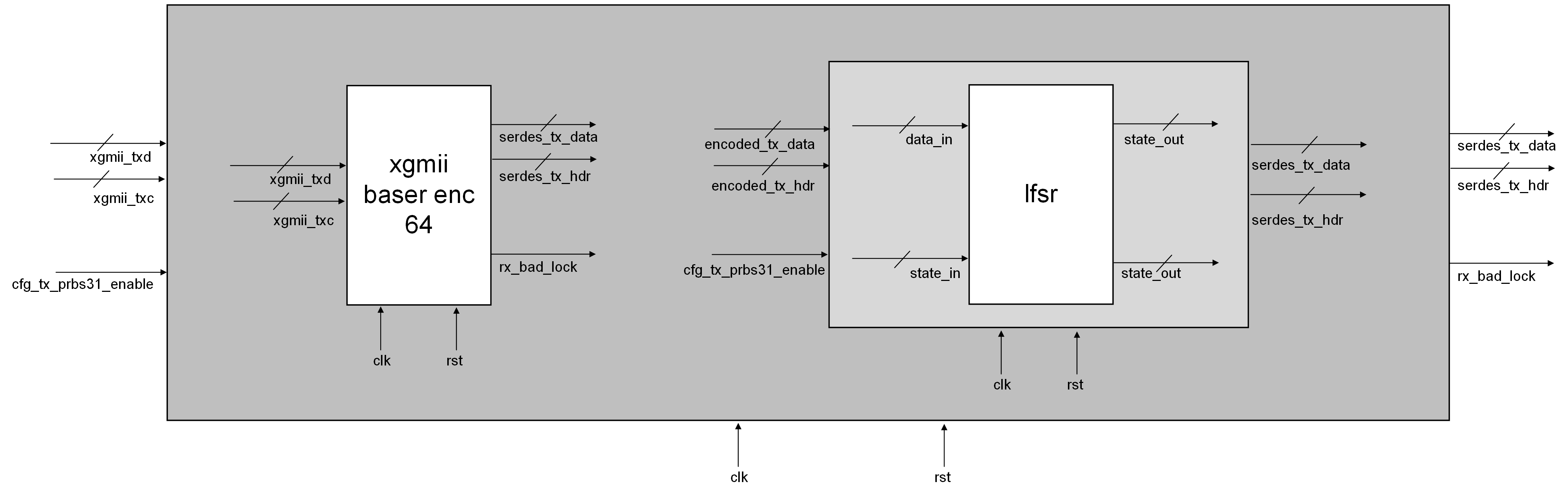

Diagram

DATA_WIDTH CTRL_WIDTH HDR_WIDTH BIT_REVERSE SCRAMBLER_DISABLE PRBS31_ENABLE SERDES_PIPELINE wire clk wire rst wire [CTRL_WIDTH-1:0] xgmii_txc wire cfg_tx_prbs31_enable wire [DATA_WIDTH-1:0] serdes_tx_data wire [HDR_WIDTH-1:0] serdes_tx_hdr wire tx_bad_block

Hierarchical structure

Description

Modulo del transmisor de 10g

Generics

Generic name

Type

Value

Description

DATA_WIDTH

64

Ancho de datos

CTRL_WIDTH

(DATA_WIDTH/8)

Ancho de control

HDR_WIDTH

2

Ancho de header

BIT_REVERSE

0

Flag que habilita la inversión de bits

SCRAMBLER_DISABLE

0

Flag que habilita el scrambler

PRBS31_ENABLE

0

Flag que habilita la generacion de patrones pseudoaleatorios PRBS31

SERDES_PIPELINE

0

Flag que habilita el uso de pipeline en el SERDES

Ports

Port name

Direction

Type

Description

clk

input

wire

Señal de clock

rst

input

wire

Señal de reset

xgmii_txc

input

wire [CTRL_WIDTH-1:0]

Señales de control de la interfaz XGMII

serdes_tx_data

output

wire [DATA_WIDTH-1:0]

Datos de salida para SERDES

serdes_tx_hdr

output

wire [HDR_WIDTH-1:0]

Header de salida para SERDES

tx_bad_block

output

wire

Señal de estado para indicar un bloque defectuoso durante la transmisión

cfg_tx_prbs31_enable

input

wire

Entrada para habilitar la generacion de patrones PRBS31

Signals

Name

Type

Description

encoded_tx_data

wire [DATA_WIDTH-1:0]

Señal para datos codificados

encoded_tx_hdr

wire [HDR_WIDTH-1:0]

Señal para encabezado codificado

Instantiations

xgmii_baser_enc_inst: xgmii_baser_enc_64

Instancia de modulo para la codificacion de datos segun estandar XGMII

eth_phy_10g_tx_if_inst: eth_phy_10g_tx_if

Instancia para la recepción de datos codificados desde la capa XGMII , la configuración de la transmisión según parámetros como el bit reverse, la habilitación o deshabilitación de scrambler y la generación de PRBS31, así como la transmisión de estos datos codificados y la configuración del SERDES